3D Metal Printing System

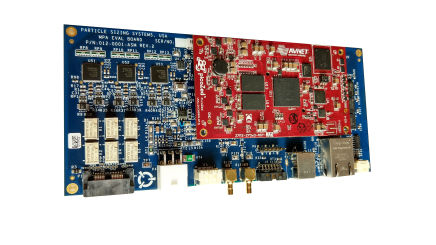

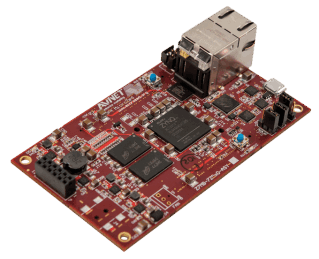

Verien led a team of four in the design of a 3D metal printing system which consisted of two FPGA designs, three board designs, and mechanical enclosures. The main FPGA is a Zynq Ultrascale+ MPSoC with six ARM cores running the application, with communications over Gigabit Ethernet and two Powerlink nodes allowing for real time synchronization and system expansion. This FPGA communicated to the second board with three Artix-7 FPGAs which implemented the laser interfaces.

The main FPGA interfaces to encoders for position information and receives packets of laser descriptors which specify firing the lasers using PWM with 10 nsecs of accuracy. All of this may be replicated and operated in synchronization allowing for modularization that controls an array of over 150 high powered lasers.

The system contains many essential interfaces: status and control of multiple 10KW power supplies to power the lasers, laser status and power monitoring, laser safety interlock, laser current control, the cooling subsystem, SATA (eMMC) drive, and others.