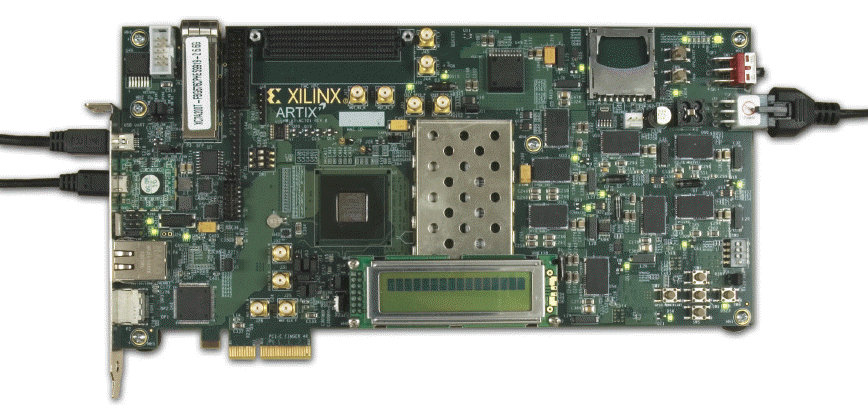

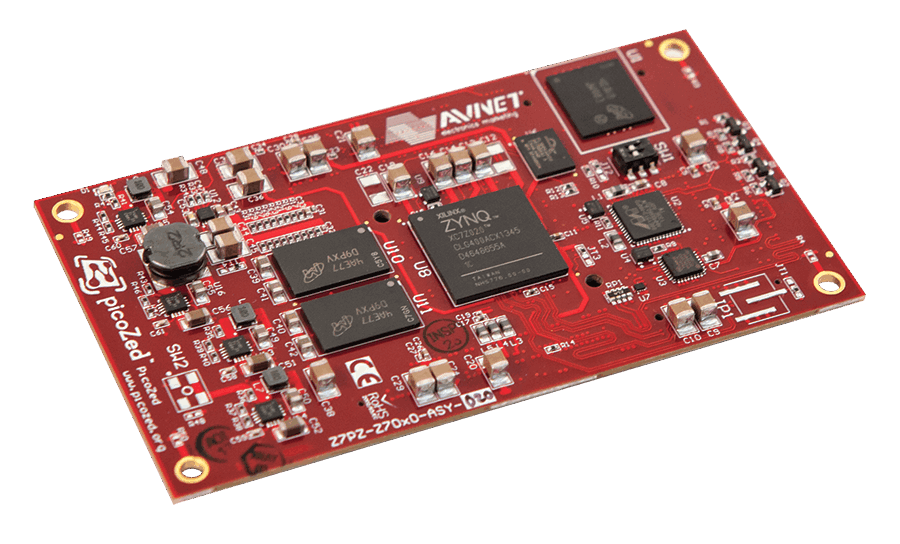

These SOC cards generally contain a high-density connector which provides the connections to the FPGA fabric and the I/O (Gigabit Ethernet, USB, serial I/O, PWM, SPI, etc). Cards like the PicoZED are referred to as System On Modules (SOMs) which require a carrier card for power and the I/O connectors. The vendors provide generic carrier cards which can be used to create a development platform.

One of the challenges when developing a POC system is when the final product is a data acquisition system, that is, it contains ADCs which won't be available in an off-the-shelf evaluation card. In this case, it may be possible algorithmically generate the ADC data in the FPGA, or to download the data to the card prior to running the application.

By using an evaluation card as a POC system, generally some portion of the FPGA design needs to be completed, but while the actual hardware (PCB design) may be months from completion, the debug of the software can get started months early using the POC system. The POC system will be software compatible with the final hardware since it’s basically the same FPGA design – a huge advantage.