Zynq Based Magnetometer

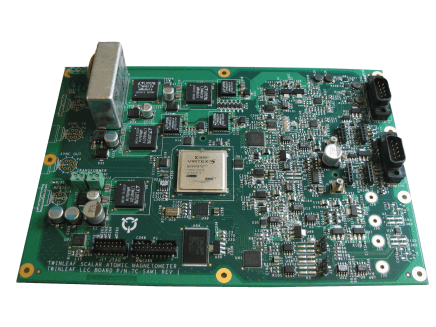

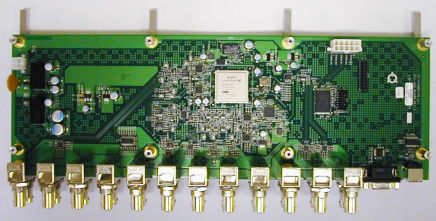

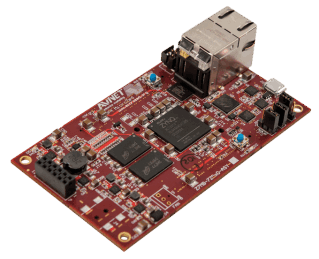

This client desired a magnetometer based on the Xilinx Zynq SOC. The Zynq contains dual ARM-9 processors, Gigabit Ethernet, USB, and a host of other features along with a generous helping of programmable logic. This design was based on custom carrier cards for the MicroZED (pictured) running Linux and communicating to the host using Ethernet and USB. The FPGA functions include: modulation of the sensor via Direct Digital Synthesis (DDS), acquisition, IIR filtering, and demodulation using lock-in amplifiers, and control of multiple precision sensor heaters and other custom interfaces. Interfaces include the AD7176 ADC, AD7193 ADC, LTC2378 ADC, and AD5541A DAC. A specialized communications scheme was developed to allow synchronization and host access in a multi-board system.